Altera’s DSP Builder tool provides MathWorks Simulink design blocks and the ability to auto-generate HDL code. The cookie is set by the GDPR Cookie Consent plugin and is used to store whether or not user has consented to the use of cookies. Altera DSP Builder Introduction The complexity of HDL coding can be a barrier for power electronics engineers. Introduction Using the Altera® DSP Builder Advanced Blockset Subsystem block, or DSPBA Subsystem block, enables you to model designs using blocks from both Simulink® and Altera®, and to automatically generate integrated HDL code.

#ALTERA DSP BUILDER EXAMPLES HOW TO#

The cookie is used to store the user consent for the cookies in the category "Performance". This example shows how to use the Altera® DSP Builder Advanced Blockset with HDL Coder. This cookie is set by GDPR Cookie Consent plugin. The cookie is used to store the user consent for the cookies in the category "Other. The cookies is used to store the user consent for the cookies in the category "Necessary". The cookie is set by GDPR cookie consent to record the user consent for the cookies in the category "Functional". The cookie is used to store the user consent for the cookies in the category "Analytics". These cookies ensure basic functionalities and security features of the website, anonymously. For more information, see Necessary cookies are absolutely essential for the website to function properly.

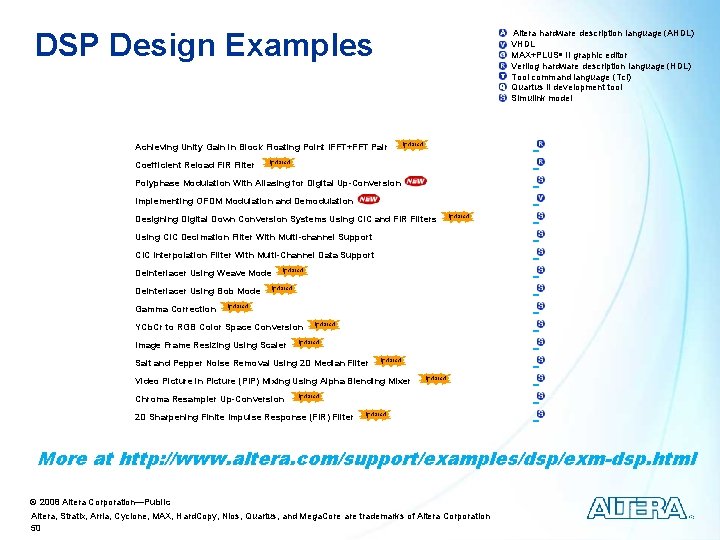

as you can see after simulation, the pic resultant (border detector) is 10pixels moved to the right, this is a problem because it can't be correlated with the original pic. DSP Builder version 8.0 includes design examples for multi-antenna, multi-carrier WiMAX and WCDMA DUC and DDC designs.ĭSP Builder 8.0 is available now. I've just finished installing DSP builder 8.0, I've load the follow file: c:\altera\80\quartus\dspbuilder\designexamples\tutorials\SOPCBuilder\AvalonFIFO. DSP Builder 8.0 also supports design scaling, allowing designers to quickly change the number of channels processed by filters and other blocks.ĭSP Builder 8.0 targets functions such as digital upconversion (DUC), downcoversion (DDC), crest factor reduction (CFR) and digital predistortion (DPD). Specifically, DSP Builder 8.0 automatically adds pipelined stages and registers to meet user-specified clock rates, and implements time division multiplexing to share resources such as multipliers. While Altera and its competitors have offered DSP synthesis tools for several years, DSP Builder 8.0 offers several unique features that boost performance.

#ALTERA DSP BUILDER EXAMPLES CODE#

San Jose, CA -Altera Corporation's DSP Builder 8.0, the first tool to generate timing-optimized RTL code from Simulink designs. For a related how-to article, see Timing-driven Simulink FPGA synthesis.